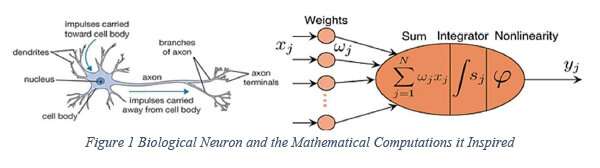

Neurona biológica y los cálculos matemáticos que inspiró. Crédito: Revista IEEE de temas seleccionados en electrónica cuántica (2022). DOI: 10.1109/JSTQE.2022.3211453

El argumento a favor de la construcción de redes neuromórficas escalables es el siguiente: al igual que los humanos, los chips más inteligentes tienen una red neuronal más grande y estrecha. De hecho, las redes neuronales son el estado del arte actual para el aprendizaje automático. Esto no es robótica, donde un brazo no sensible sigue instrucciones explícitas. En cambio, el aprendizaje automático utiliza algoritmos y modelos estadísticos para analizar y luego extraer inferencias de patrones en los datos.

Incluso unas pocas neuronas unidas pueden hacer cosas pequeñas e impresionantes. Aunque se necesita más. Entonces, un equipo de Nueva Jersey y Kingston, Ontario, elaboró un documento que cubre lo que se necesitará para obtener una escalabilidad real para la toma de decisiones basada en chips.

La respuesta propuesta es una nueva arquitectura de sistema de red neuronal fotónica con conmutación de longitud de onda (WS-PNN). La primera parte del documento nos lleva a los conceptos básicos, luego describe los beneficios de la escalabilidad plana y la flexibilidad que proviene de la integración de topologías seleccionadas.

El progreso en la escalabilidad requiere hardware de circuito integrado fotónico por una serie de razones, la más importante es la velocidad de la luz. Una arquitectura de computadora neuromórfica ejecuta los cálculos de manera paralela y distribuida, sopesa los resultados de estos cálculos, los suma, realiza una operación no lineal para la suma antes de enviar la salida a muchas otras neuronas, y finalmente obtiene la mejor respuesta de su clase. . Al igual que tus neuronas cuando estabas en clases, ¿verdad? Bien.

Las neuronas basadas en silicio se agrupan en capas, con neuronas conectadas solo a neuronas en capas adyacentes. El beneficio de una arquitectura de red neuronal en capas es que permite trucos matemáticos de álgebra lineal que aceleran los cálculos. Hay diferentes tipos de capas y topologías para elegir. Cada tipo de red neuronal sobresale en la resolución de un dominio específico de problemas, y cada uno está sintonizado con hiperparámetros que optimizan esas soluciones (la diversidad es buena).

Hablando de diversidad, el documento incluye una discusión de dos tipos de neuronas fotónicas: tipo sin picos con un modulador de microanillo y una fuente de luz externa, y neuronas con picos que usan láseres excitables. Las opciones de topología incluyen neuronas fotónicas de un solo grupo y de dos grupos.

El documento ilustra las topologías de redes neuronales expandidas antes de la ponderación de los resultados mencionados anteriormente, para lograr la escalabilidad de las redes neuronales con un número fijo de longitudes de onda. La flexibilidad que proviene de mezclar diferentes topologías admite una amplia gama de aplicaciones de aprendizaje automático (es decir, procesamiento de señales sofisticado).

El enfoque del documento en el aprendizaje automático de aplicaciones conduce directamente al uso de resonadores de microanillo (MMR) en el diseño del circuito del chip. Los resonadores de microanillo no solo se utilizan para el procesamiento de señales ópticas en una red neuronal, sino que también pueden proporcionar conmutación reconfigurable.

La reconfigurabilidad mueve la fotónica de silicio a lo largo de un camino como el chip de especialidad electrónica (ASIC) que evoluciona hacia una matriz de puerta programable de campo (FPGA). Seamos realistas: las ventajas de la programabilidad son decisivas cuando los sistemas crecen en complejidad. Además, los chips especiales son caros y tardan años en fabricarse. La escalabilidad con un número fijo de longitudes de onda puede ser el boleto.

El documento propone la adopción de conmutadores selectivos de longitud de onda (WSS) dentro de lo que se denomina el bucle de transmisión para una red neuronal fotónica de conmutación de longitud de onda (WS-PNN). La arquitectura WS-PNN puede admitir la interconexión de muchas redes neuronales fotónicas mediante la conexión de múltiples chips PNN con WSS fuera del chip.

Se espera que la arquitectura WS-PNN encuentre nuevas aplicaciones al usar interruptores WSS fuera del chip para interconectar grupos de neuronas fotónicas. La interconexión de WS-PNN puede lograr una escalabilidad sin precedentes de las redes neuronales fotónicas al tiempo que admite una selección versátil de topologías de redes neuronales recurrentes y de avance.

La investigación se publica en el Revista IEEE de temas seleccionados en electrónica cuántica.

Más información:

Lei Xu et al, Redes escalables de circuitos integrados fotónicos neuromórficos, Revista IEEE de temas seleccionados en electrónica cuántica (2022). DOI: 10.1109/JSTQE.2022.3211453

Proporcionado por el Instituto de Ingenieros Eléctricos y Electrónicos

Citación: Examen de lo que se necesita para obtener una escalabilidad real para la toma de decisiones basada en chips (31 de marzo de 2023) consultado el 31 de marzo de 2023 en https://techxplore.com/news/2023-03-real-scalability-chip-based -toma de decisiones.html

Este documento está sujeto a derechos de autor. Aparte de cualquier trato justo con fines de estudio o investigación privados, ninguna parte puede reproducirse sin el permiso por escrito. El contenido se proporciona únicamente con fines informativos.