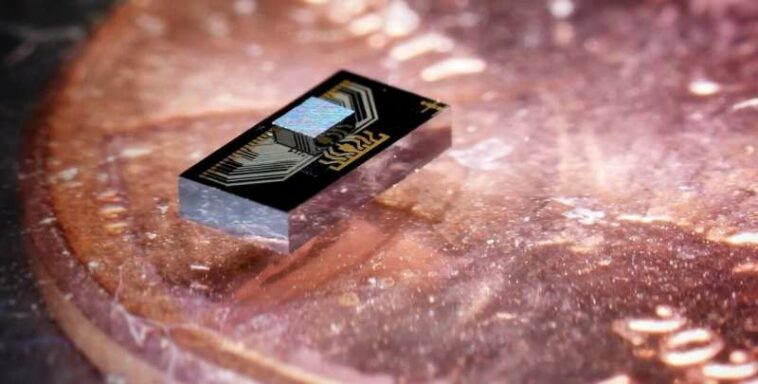

El sándwich de chip: un chip electrónico (el chip más pequeño en la parte superior) integrado con un chip fotónico, colocado encima de un centavo a modo de escala. Crédito: Arian Hashemi Talkhooncheh

Los ingenieros de Caltech y la Universidad de Southampton en Inglaterra han diseñado en colaboración un chip electrónico integrado con un chip fotónico (que utiliza la luz para transferir datos), creando un producto final cohesivo capaz de transmitir información a ultra alta velocidad mientras genera un calor mínimo.

Aunque es poco probable que el sándwich de dos chips llegue a su computadora portátil, el nuevo diseño podría influir en el futuro de los centros de datos que manejan volúmenes muy altos de comunicación de datos.

«Cada vez que está en una videollamada, transmite una película o juega un videojuego en línea, está enrutando datos de un lado a otro a través de un centro de datos para ser procesados», dice el estudiante graduado de Caltech Arian Hashemi Talkhooncheh, autor principal de un documento que describe la innovación de dos chips que se publicó en el Revista IEEE de circuitos de estado sólido el 3 de noviembre.

«Hay más de 2700 centros de datos en los EE. UU. y más de 8000 en todo el mundo, con torres de servidores apilados uno encima del otro para administrar la carga de miles de terabytes de datos que entran y salen cada segundo».

Así como su computadora portátil se calienta en su regazo mientras la usa, las torres de servidores en los centros de datos que nos mantienen a todos conectados también se calientan mientras trabajan, solo que a una escala mucho mayor. Algunos centros de datos incluso se construyen bajo el agua para enfriar toda la instalación más fácilmente. Cuanto más eficientes puedan hacerse, menos calor generarán y, en última instancia, mayor será el volumen de información que podrán gestionar.

El procesamiento de datos se realiza en circuitos electrónicos, mientras que la transmisión de datos se realiza de manera más eficiente mediante fotónica. Lograr una velocidad ultraalta en cada dominio es un gran desafío, pero diseñar la interfaz entre ellos es aún más difícil.

«Existe una demanda continua para aumentar la velocidad de la comunicación de datos entre diferentes chips no solo en los centros de datos sino también en las computadoras de alto rendimiento. A medida que aumenta la potencia de cómputo de los chips, la velocidad de comunicación puede convertirse en un cuello de botella, especialmente bajo condiciones de energía estrictas». limitaciones», dice Azita Emami, profesora Andrew y Peggy Cherng de ingeniería eléctrica e ingeniería médica; director ejecutivo de ingeniería eléctrica; y autor principal del artículo.

Para hacer frente a este desafío, el equipo de Caltech/Southampton diseñó un chip electrónico y un chip fotónico desde cero y los cooptimizó para trabajar juntos. El proceso, desde la idea inicial hasta la prueba final en el laboratorio, tardó cuatro años en completarse, y cada elección de diseño impactó en ambos chips.

«Tuvimos que optimizar todo el sistema al mismo tiempo, lo que permitió lograr una eficiencia energética superior», dice Hashemi. «Estos dos chips están literalmente hechos el uno para el otro, integrados uno en el otro en tres dimensiones».

La interfaz optimizada resultante entre los dos chips les permite transmitir 100 gigabits de datos por segundo mientras producen solo 2,4 picojulios por bit transmitido. Esto mejora la eficiencia de potencia electro-óptica de la transmisión por un factor de 3,6 en comparación con el estado actual de la técnica. Un picojulio es una billonésima parte de un julio, que se define como la energía liberada en un segundo por una corriente de 1 amperio a través de una resistencia de 1 ohmio, o alrededor de 0,24 calorías.

«A medida que el mundo se vuelve cada vez más conectado y cada dispositivo genera más datos, es emocionante demostrar que podemos lograr tasas de datos tan altas mientras quemamos una fracción de energía en comparación con las técnicas tradicionales», dice Emami.

El documento se titula «Un transmisor óptico PAM4 de 100 Gb/s en una plataforma SiPh-CMOS integrada en 3D que utiliza moduladores MOSCAP segmentados».

Arian Hashemi Talkhooncheh et al, un transmisor óptico PAM4 de 100 Gb/s en una plataforma SiPh-CMOS integrada en 3D que utiliza moduladores MOSCAP segmentados, Revista IEEE de circuitos de estado sólido (2022). DOI: 10.1109/JSSC.2022.3210906

Citación: El sándwich de chip electrónico/fotónico empuja los límites de la eficiencia informática y de transmisión de datos (2022, 18 de noviembre) recuperado el 18 de noviembre de 2022 de https://techxplore.com/news/2022-11-electronicphotonic-chip-sandwich-boundaries-transmission.html

Este documento está sujeto a derechos de autor. Aparte de cualquier trato justo con fines de estudio o investigación privados, ninguna parte puede reproducirse sin el permiso por escrito. El contenido se proporciona únicamente con fines informativos.