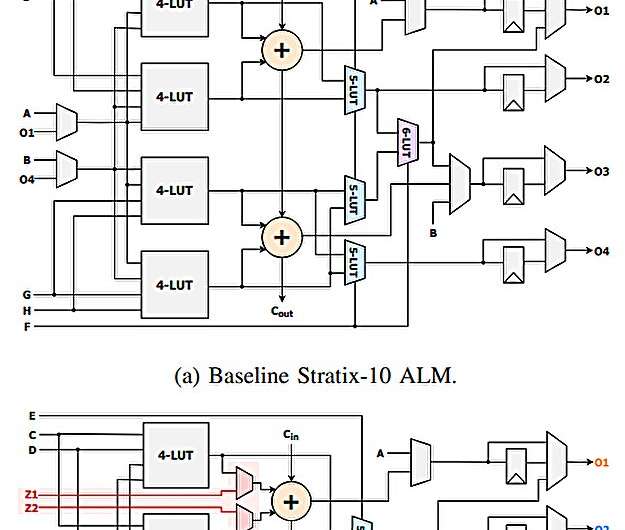

Basario (a) y arquitecturas ALM de doble servicio. Mostramos dos variantes: el DD5 (b) admite el uso concurrente de 5-LUT y los admiradores, mientras que el DD6 (c) admite el uso concurrente de 6- LUT y Adder. Crédito: arxiv (2025). Doi: 10.48550/arxiv.2507.11709

Una nueva innovación de los investigadores de Cornell reduce el uso de energía necesaria para alimentar la inteligencia artificial, un paso para reducir las huellas de carbono de los centros de datos e infraestructura de IA.

A medida que los sistemas de IA se vuelven cada vez más poderosos, también se vuelven más hambrientos de poder, que crían preguntas urgentes sobre la sostenibilidad. El equipo de investigación, de Cornell Tech y Cornell Engineering, está abordando ese desafío al repensar el hardware que alimenta la IA, con el objetivo de hacerlo más rápido, más eficiente y menos intensivo en energía.

Los investigadores recibieron un Premio al mejor papel Para sus hallazgos, presentada en la Conferencia Internacional sobre Lógica y Aplicaciones de Field Programable (FPL 2025), celebrado del 1 al 5 de septiembre en Leiden, Países Bajos. El papel es disponible en el arxiv servidor de preimpresión.

Su trabajo se centra en un tipo de chip de computadora llamado una matriz de compuerta programable de campo (FPGA). Estos chips son apreciados por su flexibilidad: a diferencia de los chips tradicionales, se pueden reprogramarse para diferentes tareas después de la fabricación. Esto los hace especialmente útiles en campos en rápida evolución, como IA, computación en la nube y comunicación inalámbrica.

«Los FPGA están en todas partes, desde tarjetas de red y estaciones base de comunicación hasta máquinas de ultrasonido, escaneos de gatos e incluso lavadoras», dijo el coautor Mohamed Abdelfattah, profesor asistente de Cornell Tech. «La IA está llegando a todos estos dispositivos, y esta arquitectura ayuda a que esa transición sea más eficiente»,

Dentro de cada chip FPGA hay unidades de computación llamadas bloques lógicos. Estos bloques contienen componentes que pueden manejar diferentes tipos de computación. Las tablas de búsqueda (LUT) son componentes que pueden realizar una amplia gama de operaciones lógicas dependiendo de lo que el chip debe hacer. Las cadenas de sumas son componentes que realizan operaciones aritméticas rápidas, como agregar números, esencial para tareas como el reconocimiento de imágenes y el procesamiento del lenguaje natural.

En los diseños convencionales de FPGA, estos componentes están estrechamente vinculados, lo que significa que solo se puede acceder a las cadenas de sumador a través de las LUT. Esto limita la eficiencia del chip, especialmente para las cargas de trabajo de IA que dependen en gran medida de las operaciones aritméticas.

El equipo de investigación desarrolló «Double Duty», una nueva arquitectura de chips, para abordar este problema. El diseño permite que LUTS y las cadenas de sumador funcionen de forma independiente y simultáneamente dentro del mismo bloque lógico. En otras palabras, el chip ahora puede hacer más con exactamente los mismos recursos de procesamiento.

Esta innovación es particularmente impactante para las redes neuronales profundas, modelos de IA que imitan el procesamiento de información del cerebro humano. Estos modelos a menudo se «desenrollan» a los FPGA, aportados como circuitos fijos para un procesamiento más rápido y eficiente.

«Nos centramos en un modo en el que los FPGA son realmente buenos en la aceleración de la IA», dijo Abdelfattah, quien también está afiliado a Cornell Engineering. «Al hacer un pequeño cambio arquitectónico, hacemos que estas redes neuronales desenrolladas sean mucho más eficientes, jugando con las fortalezas de los FPGA en lugar de tratarlas como procesadores genéricos».

En las pruebas, el diseño de doble trabajo redujo el espacio necesario para tareas de IA específicas en más del 20% y mejoró el rendimiento general en un gran conjunto de circuitos en casi un 10%. Eso significa que se podrían usar menos chips para realizar el mismo trabajo, lo que resulta en un menor uso de energía.

El impacto va más allá de la IA. «Este cambio también beneficia a las industrias tradicionales», dijo Xilai Dai, estudiante de doctorado en ingeniería eléctrica e informática y uno de los autores principales del artículo. «Ayuda con la verificación de chips, la comunicación inalámbrica y cualquier aplicación que use la aritmética. Puede ajustar programas más grandes en chips más pequeños, lo que mejora la eficiencia en todos los ámbitos».

El trabajo comenzó como un proyecto de investigación de pregrado por DAI, quien continuó desarrollando la idea en un estudio a gran escala durante sus estudios en Cornell. El otro coautor principal del artículo, Junius Pun, ex pasante de investigación de Cornell Tech y recién graduado de la Universidad Tecnológica de Nanyang, también jugó un papel clave en el trabajo de arquitectura y modelado.

El proyecto también incluyó investigadores de la Universidad de Toronto y la Universidad de Waterloo, así como ingenieros de Altera (anteriormente parte de Intel).

«Fue una gran colaboración entre socios académicos y la industria, con muchas piezas móviles», dijo Abdelfattah. «Es un paso hacia el uso de FPGA de una manera que juega con sus fortalezas, haciéndolos dispositivos informáticos verdaderamente eficientes».

Más información:

Junius Pun et al, Double Duty: FPGA Architecture para permitir el uso concurrente de la cadena LUT y Adder, arxiv (2025). Doi: 10.48550/arxiv.2507.11709

Citación: El nuevo diseño de chip corta el uso de energía de IA al habilitar el procesamiento FPGA más inteligente (2025, 15 de septiembre) Consultado el 15 de septiembre de 2025 de https://techxplore.com/news/2025-09-ai-hardware-reimagined-energy.html

Este documento está sujeto a derechos de autor. Además de cualquier trato justo con el propósito de estudio o investigación privada, no se puede reproducir ninguna parte sin el permiso por escrito. El contenido se proporciona solo para fines de información.