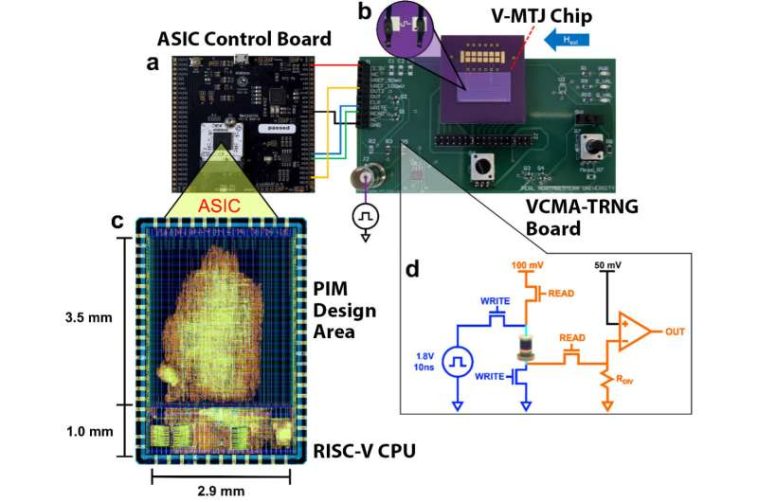

Figura que describe el sistema general, incluido el chip V-MTJ y el ASIC junto con sus respectivas placas de circuito impreso. Crédito: Duffee et al.

Las máquinas probabilísticas de ising (PIMS) son sistemas informáticos avanzados y especializados que podrían abordar problemas computacionalmente difíciles, como las tareas de optimización o factorización entera, de manera más eficiente que los sistemas clásicos. Para resolver problemas, los PIM se basan en interactuar bits probabilísticos (bits P), redes de unidades interactuantes de información digital con valores que fluctúan aleatoriamente entre 0 y 1, pero que pueden ser sesgadas para converger para producir soluciones deseadas.

Una clase de PIMS que se investigan intensamente usa dispositivos magnéticos para inyectar aleatoriedad en un circuito basado en transistores digitales. Si bien se ha encontrado que estos sistemas son prometedores para la rápida resolución de varios problemas específicos de dominio y avanzados, su diseño a gran escala y su fabricación confiable han demostrado ser desafiantes hasta ahora. Esto se debe principalmente a que su compensación requiere el control preciso de pequeños momentos magnéticos y, a menudo, también implica el uso de grandes circuitos que convierten las señales digitales en voltajes analógicos y otros componentes adicionales.

Los investigadores de la Universidad de Northwestern y otros institutos desarrollaron recientemente un nuevo circuito integrado específico de la aplicación (ASIC) que podría usarse para crear computadoras probabilísticas de mejor rendimiento. En un papel publicado en Electrónica de la naturalezapresentaron una computadora probabilística basada en el nuevo circuito y mostraron que podría realizar tareas de factorización entera.

«Estábamos interesados en explorar cómo se podía construir una computadora probabilística escalable mediante el diseño personalizado de un ASIC utilizando la tecnología CMOS Foundry», dijo a Tech Xplore Pedram Khalili Amiri, autor principal del documento.

«Nuestra intuición fue que al aprovechar la plataforma CMOS digital y las altas densidades de transistores disponibles en la tecnología de semiconductores actuales, uno eventualmente podría construir computadoras probabilísticas a gran escala que pueden abordar los problemas relacionados con, por ejemplo, la optimización combinatoria. Como primer paso, decidimos probar estas ideas y desarrollar la arquitectura y el enfoque de designación, utilizando un enfoque menos avanzado (130 nm nm, encontramos el nodo de omry»).

Al revisar la literatura anterior en el campo y experimentar con arquitecturas de computación probabilística, Amiri y sus colegas se dieron cuenta de que, a pesar de sus numerosas ventajas, la tecnología CMOS no parece ser adecuada para crear secuencias de bits aleatorias. En particular, la creación de estas secuencias aleatorias es fundamental para el funcionamiento de las computadoras probabilísticas.

Para superar esta limitación de la tecnología CMOS, los investigadores adaptaron las uniones de túnel magnéticas controladas por voltaje (V-MTJ), componentes de hardware que introdujeron en su trabajo anterior y previamente se habían aplicado a la creación de dispositivos de memoria de acceso aleatorio (MRAM) magnéticos. Cambiaron algunos elementos de estos dispositivos para que sirvieran como fuentes de aleatoriedad de alto rendimiento y compactos (es decir, entropía).

«Nuestra computadora probabilística consiste en una serie de elementos probabilísticos biestables (llamados bits probabilísticos o bits P)», explicó Amiri. «Las interacciones entre estos p-bits se pueden programar para que la red P-bit (llamada máquina de ising probabilísticas o PIM) busque colectivamente el espacio de solución de un problema. Nuestros bits P se implementan utilizando circuitos CMOS digitales en nuestro ASIC y usan secuencias de bits que se lee a partir de un chip V-MTJ adyacente para proporcionar la aleatoriedad requerida. La energía mínima PIM está diseñada para corresponder a la solución de la solución de la solución de COPUCTIVE.

Figura que muestra el ASIC que se usó en este experimento. Crédito: Duffee et al.

La nueva arquitectura probabilística desarrollada por Amiri y sus colegas en teoría podría usarse para abordar de manera eficiente muchos problemas del mundo real, incluidas varias tareas de optimización. Sin embargo, como parte de su estudio, el equipo aplicó específicamente su arquitectura a tareas de factorización entera, que se sabe que son muy difíciles de resolver computacionalmente.

«Este fue un buen lugar para comenzar, principalmente porque solo hay una solución correcta en todo el panorama energético, y porque es fácil verificar si encontramos los factores correctos o no», dijo Amiri. «Sin embargo, el mismo enfoque se puede aplicar a muchos otros problemas informáticos».

Dos ventajas centrales de la arquitectura desarrollada por este equipo de investigación son que es digital y sincrónico. Esto contrasta con la mayoría de los otros PIM introducidos en trabajos anteriores.

«Esto significa que la computadora probabilística funciona con un reloj que determina un intervalo de tiempo bien definido sobre el cual los bits P pueden actualizarse y no requiere circuitos que consumen área como convertidores digitales a analógicos», dijo Amiri. «Además, el uso de V-MTJ, que actualmente se implementan en un chip separado del ASIC, pero eventualmente se pueden integrar dentro de él, ahorra área y puede proporcionar secuencias de bits aleatorias de alto rendimiento a los bits P».

Los V-MTJS, los componentes que Amiri y sus colegas usaron para crear su arquitectura, eran inherentemente más robustos contra las variaciones de dispositivo a dispositivo cuando se usan para generar bits aleatorios en comparación con otros generadores de bits aleatorios espintrónicos utilizados en el pasado. Los hallazgos iniciales del equipo fueron muy prometedores, destacando la promesa de su enfoque para crear computadoras probabilísticas.

En particular, aunque se basa en VMTJS, el nuevo enfoque también es compatible con los procesos de fabricación CMOS establecidos y las estrategias de diseño digital. En el futuro, podría contribuir a la fabricación a gran escala de PIMS que podrían resolver una amplia gama de problemas de optimización del mundo real más rápido y de manera más eficiente.

«Nuestro próximo paso será adaptar este diseño para implementar problemas distintos de la factorización», agregó Amiri. «Por ejemplo, tenemos un chip en las obras que se adapta a otros problemas de optimización con importancia del mundo real. Además, planeamos integrar los V-MTJ directamente en el CMOS en un nodo de fundición más avanzado, lo que nos permitiría hacer que la computadora probabilística sea aún más compacta».

Escrito para usted por nuestro autor Ingrid Fadellieditado por Gaby Clarky verificado y revisado por Robert Egan—Este artículo es el resultado de un trabajo humano cuidadoso. Confiamos en lectores como usted para mantener vivo el periodismo científico independiente. Si este informe le importa, considere un donación (especialmente mensual). Obtendrás un sin publicidad cuenta como agradecimiento.

Más información:

Christian Duffee et al, una computadora probabilística integrada basada en circuitos que utiliza uniones de túnel magnéticas controladas por voltaje como su fuente de entropía, Electrónica de la naturaleza (2025). Doi: 10.1038/s41928-025-01439-6. En arxiv: Doi: 10.48550/arxiv.2412.08017

© 2025 Science X Network

Citación: Nuevo diseño aborda problemas de factorización de enteros a través de la computación probabilística digital (2025, 22 de septiembre) Recuperado el 22 de septiembre de 2025 de https://techxplore.com/news/2025-09-tackles-integer-factorization-problems-digital.html

Este documento está sujeto a derechos de autor. Además de cualquier trato justo con el propósito de estudio o investigación privada, no se puede reproducir ninguna parte sin el permiso por escrito. El contenido se proporciona solo para fines de información.