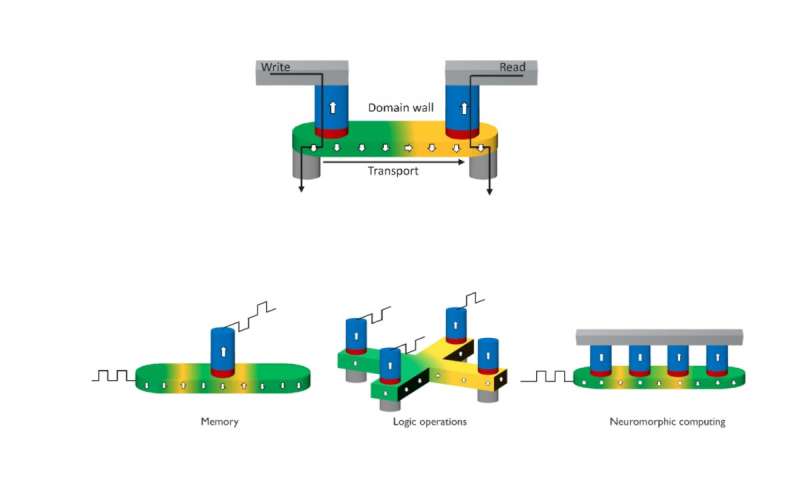

Figura 1: Esquema de (arriba) un dispositivo de pared de dominio donde los datos se pueden almacenar, pero también se pueden transportar de forma totalmente eléctrica; (abajo) aplicaciones previstas, de izquierda a derecha: memoria de pista, compuerta mayoritaria de par de giro como dispositivo lógico más allá de CMOS y generador de peso sináptico para computación neuromórfica. Crédito: IMEC

Los dispositivos de pared de dominio magnético han atraído una gran atención como un concepto de dispositivo más allá de CMOS prometedor para el escalado funcional. La tecnología basada en espintrónica podría proporcionar una plataforma donde tanto la lógica como la memoria podrían conectarse, lo que también es prometedor para la computación de memoria de entrada lógica.

En este artículo, Eline Raymenants, Van Dai Nguyen e Inge Asselberghs presentan un concepto de dispositivo único que proporciona un control eléctrico total, superando así los obstáculos prácticos para fabricar dispositivos de pared de dominio a nanoescala compatibles con CMOS.

Su trabajo se revisa en un documento IEDM invitado de 2021, que proporciona una perspectiva adicional hacia la realización de circuitos lógicos de pared de dominio complejos relevantes para la industria.

La promesa de los dispositivos de pared de dominio magnético para aplicaciones de lógica y memoria.

Mientras que la industria de los semiconductores continúa impulsando la ley de Moore en la próxima década, los institutos de investigación y el mundo académico de todo el mundo exploran formas más allá de la escala dimensional para incluir más funcionalidades por área. Un enfoque prometedor para el escalado funcional es un dispositivo de muro de dominio: un dispositivo que codifica información en dominios magnéticos. Los dominios magnéticos vecinos con diferente magnetización (indicados como ‘1’ o ‘0’) están separados por paredes de dominio magnético. La capacidad de leer y escribir estos dominios y de transportar las paredes del dominio desde la entrada hasta la salida proporciona una base interesante para construir tanto dispositivos lógicos como de memoria.

Un requisito previo para las aplicaciones lógicas es la capacidad de transferir información entre la entrada y la salida y entre diferentes puertas lógicas a una velocidad muy alta. Esto requiere un movimiento rápido de las paredes del dominio dentro de una pista de material magnético. Bajo esta condición, pueden usarse como bloques de construcción para dispositivos de puerta mayoritaria o incluso circuitos lógicos más complejos. Las puertas de la mayoría son dispositivos «democráticos» que devuelven «verdadero» (o «1») si más del 50% de sus entradas son verdaderas. En su implementación más simple, utilizan tres entradas y una salida.

En el contexto de la memoria, los dispositivos de muro de dominio se propusieron anteriormente como habilitadores para la memoria de pista de carreras, un concepto de memoria no volátil donde los muros de dominio se enrutan a través de una pista magnética hacia un número seleccionado de elementos de escritura y lectura. Estas memorias pueden alcanzar potencialmente una densidad extremadamente alta, una métrica que ahora está determinada únicamente por el material utilizado para la pista magnética.

Tener así una plataforma donde tanto la lógica como la memoria pueden conectarse (a lo largo de la misma pista magnética) ofrece una forma de ir más allá de la arquitectura tradicional de Von Neumann, donde el almacenamiento de datos y la computación están físicamente separados. Esto implica que la tecnología también tiene promesas para la computación en memoria neuromórfica.

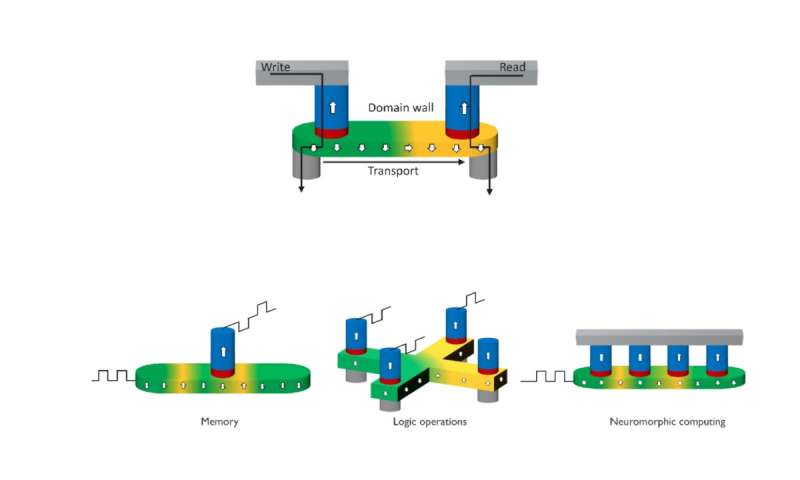

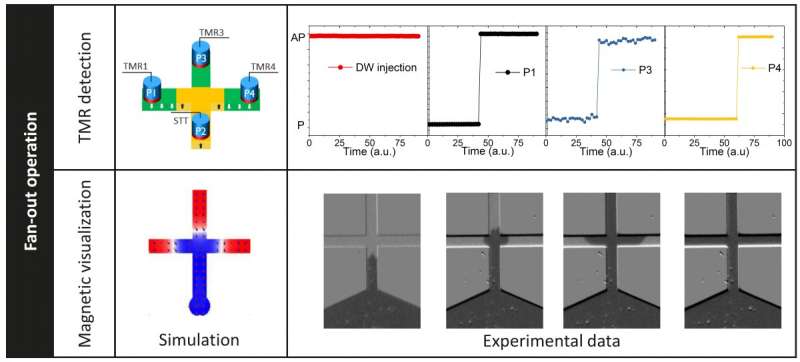

Figura 2: Diseño de capa libre híbrida para control eléctrico de dispositivos de pared de dominio e imagen TEM del dispositivo de pared de dominio de imec con dos MTJ para escritura y lectura. Los MTJ implementan una capa libre híbrida con una capa para escritura y lectura, y una capa para transferencia de muro de dominio habilitada para SOT. Crédito: IMEC

El desafío: conceptos de lectura y escritura totalmente eléctricos

La idea de utilizar dispositivos de pared de dominio magnético para aplicaciones de lógica y memoria se remonta a varias décadas. Los expertos en espintrónica han explorado diferentes conceptos de dispositivos, tanto teóricamente como en el laboratorio. Sin embargo, su trabajo se centró principalmente en explorar mecanismos en diferentes materiales para permitir un movimiento de pared de dominio rápido y eficiente. Mientras tanto, hubo menos innovación en la renovación de métodos para leer y escribir eléctricamente las paredes del dominio a nanoescala. Se basaron principalmente en el uso de campos magnéticos externos para escribir y técnicas de imágenes magnéticas para la lectura.

Sin embargo, al apuntar a dispositivos escalables compatibles con CMOS para lógica y memoria, el control eléctrico total de los dispositivos de dominio a nanoescala es esencial. Un enfoque atractivo es el uso de uniones de túnel magnéticas (MTJ) para lectura y escritura eléctricas. Los MTJ se han investigado y optimizado intensamente en el contexto del desarrollo de la tecnología de memoria magnética de acceso aleatorio (MRAM). Consisten en una fina capa dieléctrica (MgO) intercalada entre una capa magnética fija y una capa magnética libre. La variante de torque de transferencia de espín (STT) de MRAM usa una corriente para cambiar la magnetización de la capa libre (generalmente CoFeB ferromagnético). La lectura se realiza midiendo la magnetorresistencia del túnel del MTJ pasando una corriente a través de la unión.

Aunque son excelentes para leer y escribir, las pilas de material STT-MRAM tradicionales presentan graves limitaciones para el funcionamiento práctico del dispositivo de pared de dominio. En CoFeB ferromagnético, la velocidad de la pared de dominio es demasiado baja para ser aplicable a aplicaciones lógicas. Además, persisten desafíos con respecto a los pasos de modelado de grabado en el proceso de fabricación del ‘pilar’ de MTJ. La capa de CoFeB es muy susceptible al daño por grabado, lo que además dificultaría el transporte de las paredes del dominio magnético dentro de la pista.

El enfoque de Imec: una pila MTJ con capa libre híbrida

Imec ha superado los desafíos para la realización práctica de dispositivos de pared de dominio, ofreciendo un conjunto completo de componentes para leer, escribir y transportar información eléctricamente y construir dispositivos relevantes para la industria. La innovación clave es el diseño de una capa libre híbrida: una segunda capa libre específicamente para el transporte de muro de dominio se incorpora a una pila MTJ convencional. El nuevo diseño aprovecha tanto el desarrollo de la tecnología MTJ (para operaciones de lectura y escritura eficientes) como la optimización del material de transporte (para un movimiento rápido de la pared de dominio).

La primera capa libre (CoFeB) se utiliza para escribir de manera eficiente los dominios a través de STT, con lo que las paredes de dominio también se inyectan en la segunda capa de ‘transporte’ libre. Esta capa puede ser un ferromagnet o un antiferromagnet (como Pt / Co / Ru / Co). Un espaciador adicional entre las capas libres permite un acoplamiento ferromagnético eficiente entre ambas capas. Las paredes del dominio luego viajan a lo largo de la pista compartida a alta velocidad, impulsadas por el par de giro en órbita (SOT). La detección en la salida (lectura) se habilita mediante magnetorresistencia de túnel confiable.

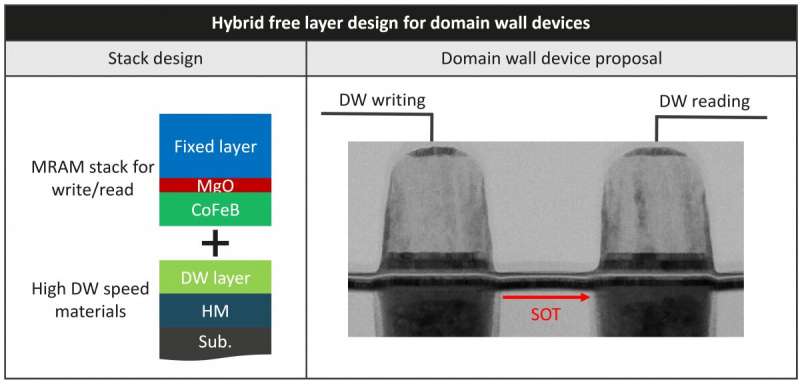

Figura 3: Demostración del funcionamiento en abanico observado mediante lectura eléctrica (TMR) en un dispositivo a nanoescala en forma de cruz, mediante simulaciones micromagnéticas y mediante técnicas de imagen magnética en dispositivos a microescala. Crédito: IMEC

Este nuevo concepto totalmente eléctrico también permite superar el desafío clave de integración relacionado con el paso de modelado de grabado MTJ. Incluso si la primera capa está dañada por el paso de modelado, las paredes del dominio aún pueden moverse dentro de la capa de transporte inferior que está más protegida del paso de grabado. Además, los dispositivos están construidos en la instalación de obleas de 300 mm de imec, utilizando procesos estándar de tecnología MRAM, lo que facilita en gran medida la adopción industrial de la tecnología.

En 2020 IEDM, el equipo de imec presentó la primera prueba de concepto del uso de estos dispositivos de pared de dominio magnético para aplicaciones lógicas. Varios MTJ, que actúan como entradas lógicas, se configuraron para alimentar puertas lógicas Y y O simples.

Estos desarrollos recientes se revisan en el artículo invitado del IEDM de 2021 «Muros de dominio magnético: de la física a los dispositivos» por E. Raymenants et al. Los resultados clave también se han descrito en el Electrónica de la naturaleza artículo «Dispositivos de pared de dominio a nanoescala con lectura y escritura de unión de túnel magnético» por E. Raymenants et al.

Outlook: Hacia circuitos en memoria de lógica, memoria y lógica del mundo real completamente funcionales

Todavía queda un largo camino por recorrer antes de que los dispositivos de pared de dominio magnético puedan incorporarse a productos comerciales. El documento IEDM de 2021 describe los primeros pasos del equipo hacia la construcción de circuitos lógicos más complejos más allá de CMOS. En este estudio, los bloques de construcción básicos presentados anteriormente se implementan en geometrías lógicas más complejas para aprender más sobre el movimiento de la pared de dominio dentro de estas estructuras. Un ejemplo de tal geometría es una implementación de una puerta mayoritaria de par de giro (STMG), que consta de tres MTJ de entrada y una MTJ de salida. Los cuatro MTJ comparten una pista de pared de dominio en forma de cruz. El equipo no solo pudo demostrar el movimiento de la pared de dominio dentro de la pista (de acuerdo con las observaciones por imágenes magnéticas), sino que también pudo demostrar que este diseño permite la operación en abanico. El funcionamiento en abanico significa que la señal de salida de una o más puertas lógicas se puede utilizar como señal de entrada para puertas adyacentes, un requisito clave para el funcionamiento del circuito lógico.

Se planean investigaciones adicionales para prepararse para una memoria de pista de carreras de alta densidad completamente funcional. En el futuro, también será necesario desarrollar nuevas arquitecturas y algoritmos para dispositivos de memoria de entrada lógica basados en paredes de dominio.

En 2021 IEDM, imec revisa su trabajo sobre dispositivos de pared de dominio magnético destinados a escalado funcional de memoria y lógica, y para computación neuromórfica. Se demuestra un nuevo diseño de capa libre dentro de los MTJ para superar las limitaciones prácticas de los dispositivos de pared de dominio magnético de última generación. La investigación inicial para implementar los dispositivos en circuitos lógicos más complejos parece prometedora, allanando el camino hacia dispositivos espintrónicos energéticamente eficientes para aplicaciones lógicas más allá de CMOS.

El control eléctrico de dispositivos de pared de dominio basado en uniones de túnel magnéticas perpendiculares

Dispositivos de pared de dominio magnético: desde la física hasta la aplicación a nivel de sistema. hdl.handle.net/1721.1/121727

E. Raymenants et al, dispositivos de pared de dominio a nanoescala con lectura y escritura de unión de túnel magnético, Electrónica de la naturaleza (2021). DOI: 10.1038 / s41928-021-00593-x

Citación: Dispositivos de pared de dominio magnético más cercanos a la realidad industrial (2021, 13 de diciembre) recuperado el 24 de diciembre de 2021 de https://techxplore.com/news/2021-12-magnetic-domain-wall-devices-closer.html

Este documento está sujeto a derechos de autor. Aparte de cualquier trato justo con el propósito de estudio o investigación privada, ninguna parte puede ser reproducida sin el permiso por escrito. El contenido se proporciona únicamente con fines informativos.