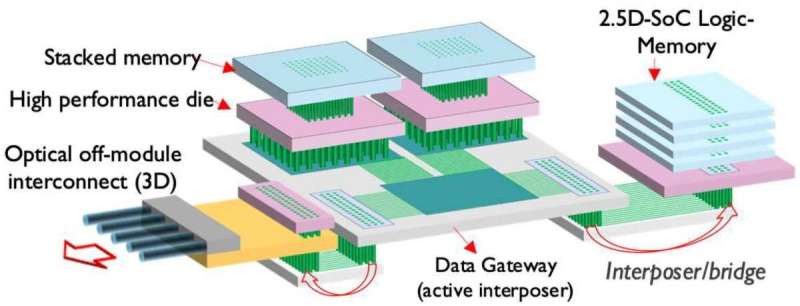

Figura 1: Vista resumida de un posible sistema futuro de alto rendimiento. La matriz de alto rendimiento con memoria apilada 3D-SOC se implementa en un chip de interposición activo que actúa como una puerta de enlace de datos y se conecta en forma de ‘2.5’ con memorias locales de gran ancho de banda y módulos de transceptor óptico (como se presentó en 2021 IEDM). Crédito: IMEC

El sistema 3D en chip (3D SOC), habilitado por la automatización del diseño electrónico (EDA) y las tecnologías de proceso 3D, es un enfoque de integración heterogéneo atractivo para abordar la pared de memoria en sistemas de alto rendimiento.

Se pueden lograr mayores ganancias de rendimiento a nivel del sistema cuando se explota la parte trasera de una de las obleas integradas para suministro de energía, enrutamiento de señal o ambos.

En este artículo, Dragomir Milojevic, Geert Van der Plas y Eric Beyne arrojan luz sobre estos enfoques prometedores.

Los beneficios del diseño 3D-SOC y de las interconexiones traseras en circuitos específicos se destacan en dos artículos presentados en la 2021 IEEE International Electron Devices Meeting (IEDM).

Promesas de un enfoque de diseño 3D-SOC

Los sistemas de alto rendimiento con uso intensivo de datos destinados a computación avanzada, servidores de datos o aplicaciones de aprendizaje profundo sufren cada vez más del llamado muro de memoria, el desafío de acceder a los datos con la suficiente rapidez. Un enfoque interesante para derribar este muro de memoria es la integración de sistema en chip 3D (3D SOC). Siguiendo este enfoque de integración heterogénea, el sistema se divide automáticamente en chips separados que se diseñan e interconectan simultáneamente en la tercera dimensión.

En su artículo invitado de IEDM de 2021 ‘Integración 3D-SOC, más allá de los chiplets 2.5D’, los autores explican cómo este concepto 3D-SOC va más allá de los enfoques de chiplet populares de hoy en día para realizar la integración de sistemas heterogéneos de varios chips. Eric Beyne, investigador senior, vicepresidente de I + D y el director del programa de integración del sistema 3D en imec: «Los chiplets implican troqueles de chiplet diseñados y procesados por separado. Un ejemplo bien conocido son las memorias de gran ancho de banda (HBM): pilas de chips de memoria dinámica de acceso aleatorio (DRAM). Esta pila de memoria se conecta a un chip de procesador a través de buses de interfaz, que limitan su uso a aplicaciones tolerantes a la latencia. Como tal, el concepto chiplet nunca permitirá un acceso rápido entre la lógica y las memorias caché de primer nivel e intermedio «.

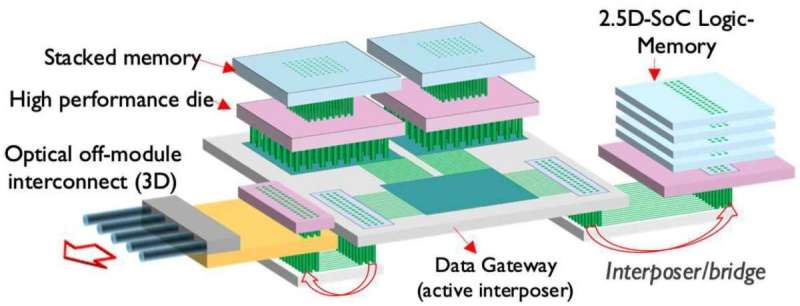

Figura 2: Unión híbrida de oblea a oblea con un tono de 700 nm (como se presentó en el IEDM de 2021). Crédito: IMEC

Con la integración 3D-SOC, las particiones de lógica de memoria se pueden realizar utilizando interconexiones directas y más cortas, lo que da como resultado mejoras significativas en el rendimiento. En su artículo invitado, los autores muestran una implementación optimizada de un diseño 3D-SOC con macros de memoria en el troquel superior y lógica restante en el troquel inferior, lo que da como resultado una frecuencia de funcionamiento un 40 por ciento más alta en comparación con un diseño 2D.

También discuten los desafíos clave de la realización de SOC 3D completamente funcionales. Dragomir Milojevic, científico principal de imec y profesor de la Université libre de Bruxelles: «Por el lado del diseño, se necesita una estrategia de codiseño 3D-SOC para particiones lógicas y de memoria. Esto requiere herramientas dedicadas de automatización del diseño electrónico (EDA) que puedan manejar ambos diseños simultáneamente, utilizando herramientas automatizadas para la partición del sistema y la optimización de la ruta crítica 3D durante el lugar y la ruta. A través de nuestra colaboración con Cadence, tenemos acceso a estas herramientas altamente avanzadas «. Por el lado de la tecnología, el progreso en las soluciones de unión híbrida de oblea a oblea permitirá densidades de interconexión de chip a chip muy altas, obligatorias para la partición de memorias caché de primer nivel e intermedio.

El siguiente paso: explotar la parte trasera de la oblea.

Una posible partición de sistemas 3D-SOC de alto rendimiento implica que algunas o todas las macros de memoria se coloquen en el troquel superior, mientras que la lógica se coloca en el troquel inferior. Por el lado de la tecnología, esto se puede lograr uniendo el anverso activo de la ‘oblea lógica’ al anverso activo de la ‘oblea de memoria’ mediante el uso de una técnica de unión de oblea a oblea a baja temperatura. En esta configuración, las partes posteriores originales de ambas obleas ahora residen en el exterior del sistema 3D-SOC.

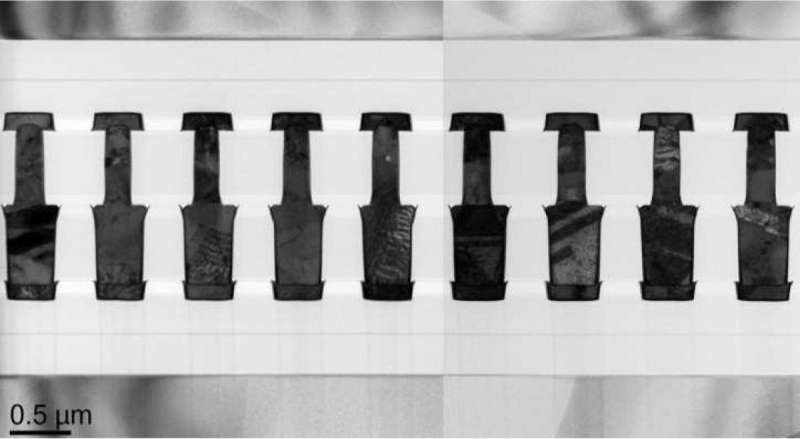

Eric Beyne: «Ahora podemos pensar en explotar la parte trasera ‘libre’ de estas obleas para enrutar la señal o para alimentar directamente los transistores en la ‘oblea lógica’. Tradicionalmente, el enrutamiento de la señal y la entrega de energía ocurren en la parte frontal de la oblea, donde compiten por el espacio en un esquema complejo de interconexiones de final de línea. En estos diseños, la parte trasera de la oblea solo sirve como portadora. En 2019, las simulaciones realizadas por Arm mostró por primera vez el impacto beneficioso de usar una red de suministro de energía trasera (BSPDN) en el diseño de una unidad central de procesamiento (CPU), que implementó un proceso de 3 nm desarrollado por imec. En este diseño, los metales de interconexión que residen en la parte trasera adelgazada de la oblea se conectó a transistores de 3 nm en la parte frontal de la oblea utilizando vías de silicio directo (TSV) que aterrizan en rieles eléctricos enterrados. Las simulaciones revelaron que este BSPDN era siete veces más eficiente que el PDN frontal tradicional «.

Figura 3: Esquema de los metales convencionales del lado frontal (FS) BEOL y del lado posterior (BS) para PDN y enrutamiento de señales. Los metales BS para el enrutamiento PDN utilizan nTSV para conectar los metales BS al riel eléctrico enterrado, mientras que los metales BS para el enrutamiento de señales usan nTSV para conectar los metales BS a los metales FS (como se presentó en 2021 IEDM). Crédito: IMEC

Por lo tanto, se pueden esperar ganancias de rendimiento adicionales cuando se implementan BSPDN para suministrar los circuitos lógicos centrales que consumen mucha energía y que residen en la parte inferior de un 3D-SOC de «memoria en lógica». También se podrían pensar en particiones 3D-SOC alternativas en las que parte de los mosaicos de memoria (por ejemplo, la memoria caché de acceso aleatorio estático (SRAM) de las memorias caché de nivel L1) también residen en la matriz inferior, también alimentada desde la parte trasera.

Además de ampliar las posibilidades para los diseños 3D-SOC, también se han propuesto BSPDN para la lógica monolítica de un solo chip y los sistemas en chip (SOC) SRAM, donde pueden ayudar en el escalado de IC y dispositivos adicionales. Geert Van der Plas, gerente de programas de imec: «Mover la red de suministro de energía a la parte trasera del chip ha demostrado ser un enfoque interesante para abordar el desafío de la congestión del enrutamiento de back-end-of-line (BEOL) y reducir la caída de IR. La diferencia con el enfoque 3D-SOC es que ahora se une una oblea ficticia a la oblea objetivo para permitir el adelgazamiento y la metalización de la oblea posterior «. Uno de los socios de imec anunció recientemente la implementación de dicho concepto BSPDN en uno de sus futuros chips de nodo.

Interconexiones traseras para mejorar aún más el rendimiento de la macro y la lógica de SRAM

Si bien los beneficios de un BSPDN ya podrían demostrarse en diseños específicos, se pueden esperar ganancias adicionales al usar la parte trasera de la oblea para el enrutamiento de señal global. Imec, en colaboración con Cadence, ha evaluado y optimizado por primera vez los diseños de circuitos lógicos y macro SRAM que se enrutan parcialmente desde la parte trasera. Una macro SRAM no solo involucra las matrices de celdas de bits de memoria, sino también los circuitos periféricos (como decodificadores de direcciones, bloques de control, etc.), lo que es relevante para el diseño del procesador.

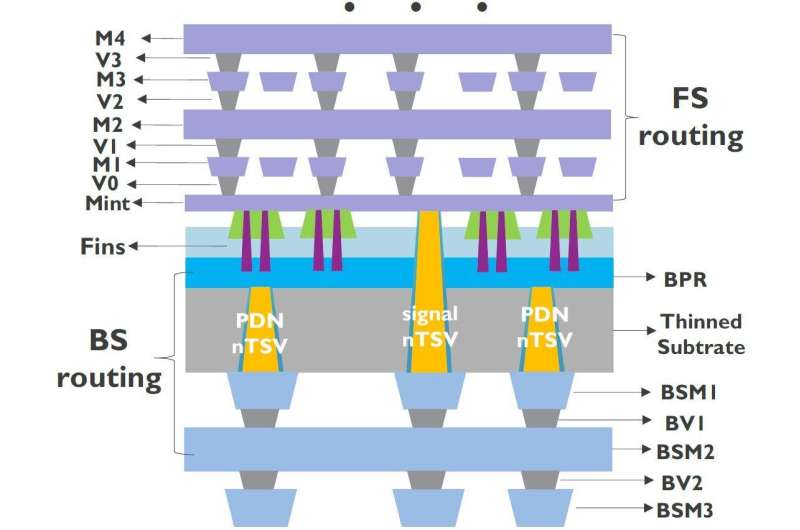

Tanto para la lógica y la macro SRAM, se utilizaron hasta tres capas de metal en la parte trasera para el enrutamiento de la señal, mientras que los nano-TSV (nTSV) conectan la metalización de la parte trasera con la parte delantera. Las macros SRAM implementaron transistores de nanohojas de 2 nm en su diseño. En estas macros, solo las rutas globales para el circuito periférico se diseñaron con metalización posterior. Por lógica, se utilizó un marco de oscilador en anillo para evaluar el impacto del enrutamiento de la señal en la parte trasera. El diseño implementó hojas de horquilla del nodo de tecnología de 2nm en las celdas lógicas estándar. Se utiliza una implementación física de una CPU ARMTM de 64 bits que utiliza el mismo kit de diseño de proceso de hoja de horquilla (PDK) de 2 nm para garantizar la significación de los resultados de la simulación del oscilador de anillo.

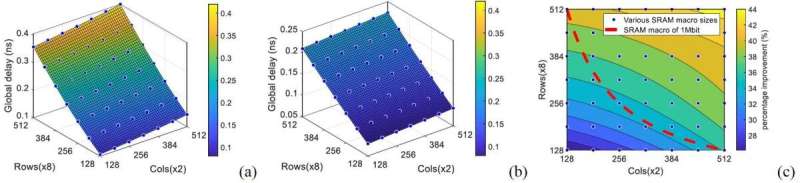

Figura 4 – Retardo de enrutamiento global (acceso de lectura) de la macro SRAM en varias filas y columnas de macro. (a) FS; (b) Mejora de BS y (c) de FS a BS. El tamaño de la macro varía de 128 * 128 * 16 = 256 kbit a 515 * 512 * 16 = 4 Mbit (como se presentó en 2021 IEDM). Crédito: IMEC

Geert Van der Plas: «En comparación con el enrutamiento frontal, el enrutamiento trasero resultó significativamente más beneficioso para mejorar el retardo y la eficiencia energética para el enrutamiento de señales de interconexión prolongada. Para las macros SRAM, demostramos una mejora del rendimiento de hasta un 44% y una eficiencia energética de hasta un 30%. mejora en comparación con el enrutamiento frontal. Para las celdas lógicas, el enrutamiento trasero permitió una mejora de la velocidad de 2.5x y un aumento de la eficiencia energética del 60 por ciento «. Los resultados se describen en el artículo del IEDM de 2021 «Diseño y optimización de la lógica y macro de SRAM utilizando interconexiones traseras en un nodo de 2 nm» de R. Chen et al.

La evaluación del rendimiento y la eficiencia energética de los circuitos se permitió mediante una combinación de experimentos y modelado. Dragomir Milojevic: «Los experimentos involucraron una optimización del procesamiento de nTSV en términos de capacitancia y resistencia, para asegurar una buena conexión eléctrica entre los metales de la parte frontal y la parte posterior. Estos parámetros se introdujeron en un modelo, utilizado para realizar las simulaciones. Finalmente, nuestro equipo realizó una optimización de enrutamiento impulsada por co-optimización de tecnología de diseño (DTCO) que mostró un camino para mejoras adicionales. Demostramos una mejora adicional del rendimiento del 20 por ciento al reducir la capacitancia de los metales de la parte trasera «.

Dispositivos de pared de dominio magnético más cercanos a la realidad industrial

Citación: Beneficios del diseño 3D-SOC y las interconexiones traseras para futuros sistemas de alto rendimiento (2021, 13 de diciembre) recuperado el 24 de diciembre de 2021 de https://techxplore.com/news/2021-12-benefits-3d-soc-backside-interconnects -future.html

Este documento está sujeto a derechos de autor. Aparte de cualquier trato justo con el propósito de estudio o investigación privada, ninguna parte puede ser reproducida sin el permiso por escrito. El contenido se proporciona únicamente con fines informativos.