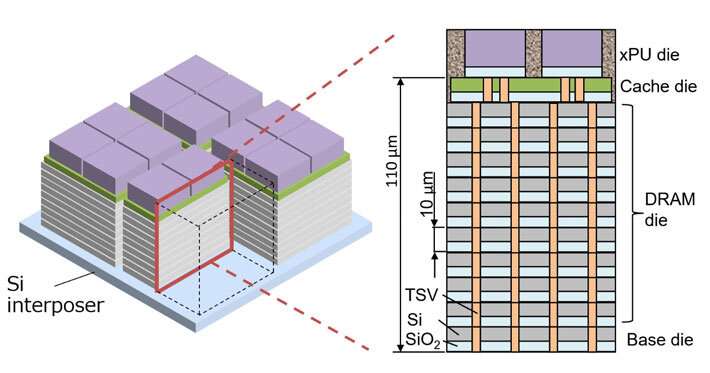

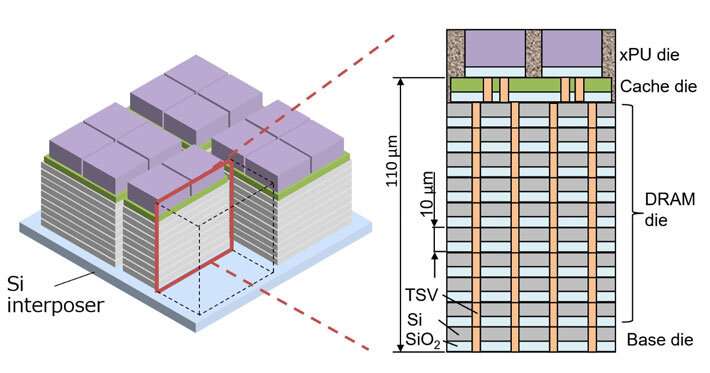

La tecnología propuesta utiliza un diseño apilado donde las unidades de procesamiento (xPU) se asientan sobre múltiples capas de memoria interconectadas (DRAM). Al reemplazar los cables con vías de silicona (TSV), las longitudes de las conexiones se pueden acortar, lo que lleva a un mejor rendimiento eléctrico general. Crédito: Instituto de Tecnología de Tokio

Una tecnología para la integración tridimensional de unidades de procesamiento y memoria, según informan investigadores de Tokyo Tech, ha logrado el mayor rendimiento posible en todo el mundo, allanando el camino hacia una computación más rápida y eficiente. Denominada «BBCube 3D», esta innovadora arquitectura apilada logra anchos de banda de datos más altos que las tecnologías de memoria de última generación, al mismo tiempo que minimiza la energía necesaria para el acceso a los bits.

En la era digital actual, los ingenieros e investigadores siguen desarrollando nuevas tecnologías asistidas por computadora que requieren mayores anchos de banda de datos entre las unidades de procesamiento (o PU, como GPU y CPU) y los chips de memoria. Algunos ejemplos de aplicaciones modernas de gran ancho de banda incluyen inteligencia artificial, simulaciones moleculares, predicción climática y análisis genético.

Sin embargo, para aumentar el ancho de banda de datos, se deben agregar más cables entre las PU y la memoria o aumentar la velocidad de datos. El primer enfoque es difícil de implementar en la práctica porque la transmisión entre los componentes mencionados anteriormente generalmente ocurre en dos dimensiones, lo que dificulta la adición de más cables. Por otro lado, aumentar la velocidad de datos requiere aumentar la energía necesaria para acceder a un bit cada vez, lo que se denomina «energía de acceso a bits», que también es un desafío.

Afortunadamente, un equipo de investigadores del Instituto de Tecnología de Tokio (Tokyo Tech) en Japón ahora puede haber encontrado una solución viable a este problema. En una reciente Simposio IEEE 2023 sobre tecnología y circuitos VLSI estudio, el profesor Takayuki Ohba y sus colegas propusieron una tecnología llamada «Bumpless Build Cube 3D» o BBCube 3D. Esta tecnología tiene el potencial de resolver los problemas mencionados anteriormente para una mejor integración entre las PU y la memoria dinámica de acceso aleatorio (DRAM).

Como sugiere el nombre, el aspecto más notable de BBCube 3D es la realización de conexiones entre PU y DRAM en tres dimensiones, en lugar de dos dimensiones. El equipo pudo lograr esta hazaña mediante el uso de una estructura apilada innovadora en la que los troqueles de PU se asientan sobre múltiples capas de DRAM, todas interconectadas a través de vías de silicio (TSV).

La arquitectura compacta general de BBCube 3D, la falta de los típicos microprotuberancias de soldadura y el uso de TSV en lugar de cables más largos contribuyen juntos a una baja capacitancia parásita y baja resistencia. Esto mejora el rendimiento eléctrico del dispositivo en varios frentes.

Además, los investigadores implementaron una estrategia innovadora que involucra entradas/salidas (IO) blindadas de cuatro fases para hacer que el BBCube 3D sea más resistente al ruido. Ajustaron la temporización de las líneas de E/S adyacentes de modo que siempre estén desfasadas entre sí, lo que significa que nunca cambian los valores simultáneamente. Esto reduce el ruido de diafonía y hace que la operación del dispositivo sea más robusta.

El equipo evaluó la velocidad de la arquitectura propuesta y la comparó con la de dos tecnologías de memoria de última generación: DDR5 y HBM2E. «El BBCube 3D tiene el potencial de lograr un ancho de banda de 1,6 terabytes por segundo, que es 30 veces más alto que DDR5 y cuatro veces más alto que HBM2E», dice el profesor Ohba, mientras explica los resultados de su experimento.

Además, BBCube 3D también representa un gran avance en términos de energía de acceso a bits. «Debido a la baja resistencia térmica y la baja impedancia de BBCube, los problemas de suministro de energía y administración térmica típicos de la integración 3D pueden aliviarse», explica el profesor Ohba, «Como resultado, la tecnología propuesta podría alcanzar un ancho de banda notable con un bit de acceso energía que es 1/20 y 1/5 de DDR5 y HBM2E, respectivamente».

Más información:

Bumpless Build Cube (BBCube) 3D: Integración 3D heterogénea usando WoW y CoW para proporcionar ancho de banda de TB/s con la energía de acceso a bits más baja. www.vlsisymposium.org/files/pr … vanceprogram0612.pdf

Citación: BBCube 3D: Implementing CPU/GPU and memory in a hybrid 3D approach (29 de junio de 2023) consultado el 29 de junio de 2023 en https://techxplore.com/news/2023-06-bbcube-3d-cpugpu-memory-hybrid. html

Este documento está sujeto a derechos de autor. Aparte de cualquier trato justo con fines de estudio o investigación privados, ninguna parte puede reproducirse sin el permiso por escrito. El contenido se proporciona únicamente con fines informativos.