BBCube: Bumless Build Cube. Una tecnología de integración tridimensional de semiconductores tridimensionales puede abordar los desafíos que plantean los enfoques tradicionales del sistema en paquetes (SIP). Crédito: Instituto de Ciencias Tokio

Se ha desarrollado una nueva tecnología de fuente de alimentación para chips integrados en 3D empleando una arquitectura informática apilada tridimensionalmente que consiste en unidades de procesamiento colocadas directamente sobre las pilas de memoria de acceso aleatorio dinámico.

Para realizar esto, los investigadores desarrollaron tecnologías clave que involucraban técnicas de unión precisas y de alta velocidad y tecnología adhesiva. Estas nuevas tecnologías pueden ayudar a abordar las demandas de aplicaciones informáticas de alto rendimiento, que requieren un alto ancho de banda de memoria y un bajo consumo de energía con un ruido de la fuente de alimentación reducida.

Desde electrodomésticos simples como televisores hasta computadoras portátiles y relojes inteligentes, los dispositivos electrónicos han transformado nuestra vida cotidiana. Los avances en las tecnologías de fabricación de semiconductores y los procesos de envasado de chips han sido fundamentales para el crecimiento explosivo de estos dispositivos electrónicos. Sin embargo, en la era actual de inteligencia artificial (IA) y la computación de alto rendimiento, la necesidad de procesadores más rápidos con una mayor eficiencia de energía permanece sin satisfacer.

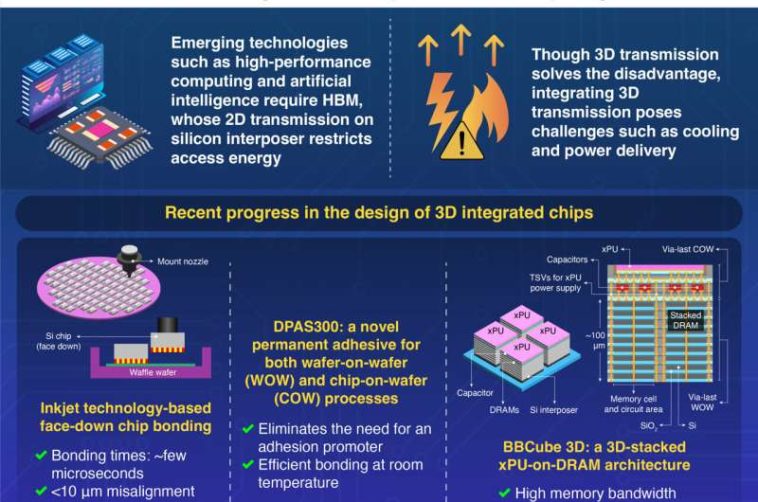

Los enfoques tradicionales del sistema en paquetes (SIP), donde los chips semiconductores se organizan en un plano bidimensional (2D) utilizando protuberancias de soldadura, tienen limitaciones relacionadas con el tamaño, lo que garantiza el desarrollo de nuevas tecnologías de integración de chips. Desde este punto de vista, un equipo de investigadores del Instituto de Ciencias Tokio (Science Tokyo), Japón, ha conceptualizado un innovador enfoque de integración de chips 2.5D/3D llamado BBCube. Además, para impulsar la realización práctica de BBCube, han desarrollado tres tecnologías clave.

Sus resultados de investigación y resultados se presentaron recientemente en el 2025 IEEE 75a Conferencia de Componentes y Tecnología Electrónica (ECTC)celebrado del 27 de mayo al 30 de mayo de 2025.

El equipo de investigación, que comprende profesores especialmente nombrados, Norio Chujo, Takayuki Ohba y otros científicos de la Unidad de Integración Heterogénea y Funcional de la Alianza WoW de la Instituto de Integración de Integrada, desarrolló inicialmente un proceso de Chip-On-Wafer (Cow) de Chip-Ofer (Cow) para el uso de las limitaciones de las entrevistas de venta vendedores.

Utilizando la tecnología de inyección de tinta y un método selectivo de recubrimiento adhesivo, llevaron a cabo con éxito unión secuencial de diferentes tamaños de chips en una oblea de gofres de 300 mm con un espacio estrecho de chip a chip de 10 μm y un tiempo de carga de montaje mínimo de menos de 10 miliseegundos.

Explicando el proceso de vaca preciso, comenta Chujo, «más de 30,000 chips de varios tamaños se fabricaron en la oblea de gofres, logrando una mayor velocidad de unión sin fallas en el deterioro de los chips».

Para habilitar este proceso de vacas preciso y de alta velocidad, los investigadores centraron su atención en abordar los problemas de estabilidad térmica que pueden afectar el apilamiento multinivel de las obleas ultra delgadas. Al diseñar cuidadosamente las propiedades químicas, desarrollaron un nuevo material adhesivo que puede usarse en procesos de vaca y oblea de oblea llamadas DPAS300. Este nuevo adhesivo, compuesto por una estructura híbrida orgánica -inorgánica, exhibió adhesividad y resistencia al calor apreciable durante los estudios experimentales.

Finalmente, para lograr un alto ancho de banda de memoria y mejorar la integridad de potencia de BBCube, los científicos emplearon una arquitectura 3D XPU-on-DRAM reforzada por una nueva carretera de distribución de energía. Esto incluyó la incrustación de condensadores entre XPU y DRAM, implementando capas de redistribución en la oblea de gofres y colocando vías a través de Silicon en carriles de obleas y líneas de escribas DRAM.

«Estas innovaciones redujeron la energía requerida para la transmisión de datos a un quinto a una vigésima parte de eso en los sistemas convencionales, al tiempo que suprimió el ruido de la fuente de alimentación a menos de 50 mV», afirma Chujo, destacando los beneficios de la arquitectura informática apilada en 3D.

En conjunto, las tecnologías de integración de chips desarrolladas por investigadores de Science Tokyo tienen el potencial de transformar las arquitecturas informáticas de próxima generación.

Más información:

BBCube 3D: integración heterogénea totalmente vertical de DRAM y XPUS utilizando una nueva carretera de distribución de energía

Citación: Método de apilamiento de chips 3D creado para superar las limitaciones tradicionales de semiconductores (2025, 20 de junio) Consultado el 25 de julio de 2025 de https://techxplore.com/news/2025-06-3d-chip-stacking-tradicional.html

Este documento está sujeto a derechos de autor. Además de cualquier trato justo con el propósito de estudio o investigación privada, no se puede reproducir ninguna parte sin el permiso por escrito. El contenido se proporciona solo para fines de información.