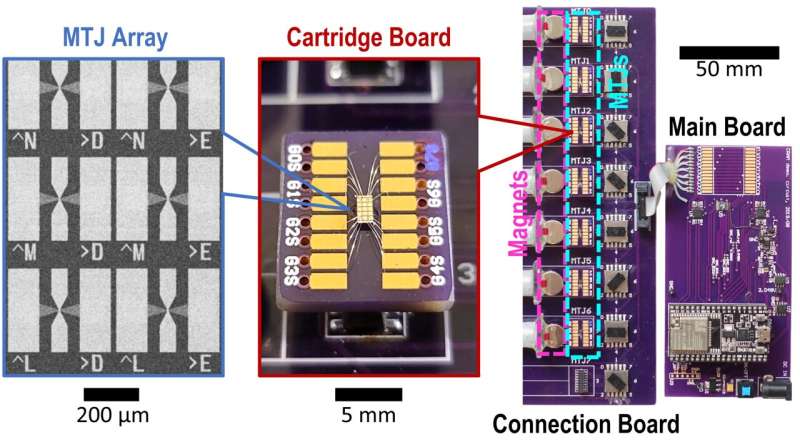

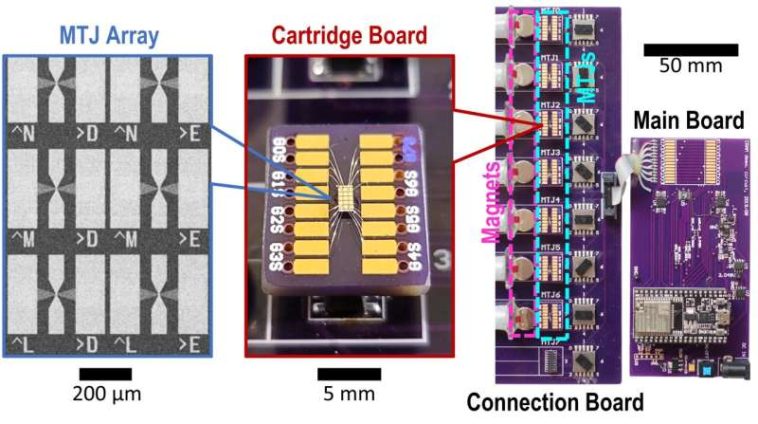

Un dispositivo de hardware diseñado a medida ayudará a que la inteligencia artificial sea más eficiente energéticamente. Crédito: Universidad de Minnesota Twin Cities.

Investigadores de ingeniería de la Universidad de Minnesota Twin Cities han demostrado un dispositivo de hardware de última generación que podría reducir el consumo de energía de las aplicaciones informáticas de inteligencia artificial (IA) en un factor de al menos 1.000.

La investigación es publicado en npj Computación no convencional El artículo se titula «Demostración experimental de una memoria computacional de acceso aleatorio basada en uniones de túnel magnético». Los investigadores tienen múltiples patentes sobre la tecnología utilizada en el dispositivo.

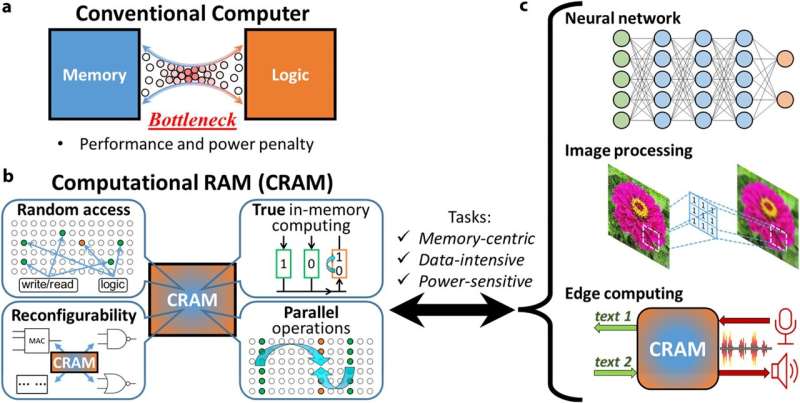

Con la creciente demanda de aplicaciones de IA, los investigadores han estado buscando formas de crear un proceso más eficiente energéticamente, manteniendo al mismo tiempo un alto rendimiento y bajos costos. Comúnmente, los procesos de máquinas o inteligencia artificial transfieren datos entre la lógica (donde se procesa la información dentro de un sistema) y la memoria (donde se almacenan los datos), consumiendo una gran cantidad de energía.

Un equipo de investigadores de la Facultad de Ciencias e Ingeniería de la Universidad de Minnesota demostró un nuevo modelo en el que los datos nunca salen de la memoria, llamada memoria de acceso aleatorio computacional (CRAM).

«Este trabajo es la primera demostración experimental de CRAM, donde los datos pueden procesarse completamente dentro de la matriz de memoria sin la necesidad de salir de la red donde una computadora almacena información», dijo Yang Lv, investigador postdoctoral del Departamento de Ingeniería Eléctrica y Computación de la Universidad de Minnesota y primer autor del artículo.

La Agencia Internacional de Energía (AIE) emitió un Pronóstico del consumo energético mundial en marzo de 2024, pronosticando que el consumo de energía para IA probablemente se duplicará de 460 teravatios-hora (TWh) en 2022 a 1.000 TWh en 2026. Esto es aproximadamente equivalente al consumo de electricidad de todo el país de Japón.

Según los autores del nuevo artículo, se estima que un acelerador de inferencia de aprendizaje automático basado en CRAM lograría una mejora del orden de 1000 veces. Otro ejemplo mostró un ahorro de energía de 2500 y 1700 veces en comparación con los métodos tradicionales.

Esta investigación se ha estado desarrollando durante más de dos décadas.

«Hace 20 años, nuestro concepto inicial de utilizar células de memoria directamente para fines informáticos se consideraba una locura», dijo Jian-Ping Wang, autor principal del artículo y profesor distinguido de la Cátedra McKnight y titular de la Cátedra Robert F. Hartmann en el Departamento de Ingeniería Eléctrica y Computación de la Universidad de Minnesota.

«Con un grupo de estudiantes en constante evolución desde 2003 y un verdadero equipo docente interdisciplinario creado en la Universidad de Minnesota (desde física, ciencia e ingeniería de materiales, informática e ingeniería hasta modelado y evaluación comparativa y creación de hardware), pudimos obtener resultados positivos y ahora hemos demostrado que este tipo de tecnología es factible y está lista para incorporarse a la tecnología», dijo Wang.

Ilustraciones del concepto, las características y las posibles aplicaciones de CRAM. Crédito: npj Computación no convencional (2024). DOI: 10.1038/s44335-024-00003-3

Esta investigación es parte de un esfuerzo coherente y de larga data que se basa en la investigación pionera y patentada de Wang y sus colaboradores sobre dispositivos de uniones de túnel magnético (MTJ), que son dispositivos nanoestructurados utilizados para mejorar discos duros, sensores y otros sistemas microelectrónicos, incluida la memoria de acceso aleatorio magnético (MRAM), que se ha utilizado en sistemas integrados como microcontroladores y relojes inteligentes.

La arquitectura CRAM permite el verdadero cálculo en y por la memoria y derriba el muro entre el cálculo y la memoria como cuello de botella en la arquitectura tradicional de von Neumann, un diseño teórico para una computadora con programa almacenado que sirve como base para casi todas las computadoras modernas.

«Como sustrato de computación en memoria basado en tecnología digital y extremadamente eficiente en términos de consumo de energía, la CRAM es muy flexible, ya que el cálculo se puede realizar en cualquier ubicación de la matriz de memoria. En consecuencia, podemos reconfigurar la CRAM para que se adapte mejor a las necesidades de rendimiento de un conjunto diverso de algoritmos de IA», afirmó Ulya Karpuzcu, experto en arquitectura informática, coautor del artículo y profesor asociado del Departamento de Ingeniería Eléctrica e Informática de la Universidad de Minnesota.

«Es más eficiente energéticamente que los bloques de construcción tradicionales para los sistemas de IA actuales».

CRAM realiza cálculos directamente dentro de las celdas de memoria, utilizando la estructura de la matriz de manera eficiente, lo que elimina la necesidad de transferencias de datos lentas y que consumen mucha energía, explicó Karpuzcu.

El dispositivo de memoria de acceso aleatorio a corto plazo (RAM) más eficiente utiliza cuatro o cinco transistores para codificar un uno o un cero, pero un MTJ, un dispositivo espintrónico, puede realizar la misma función con una fracción de la energía, con mayor velocidad y es resistente a entornos hostiles. Los dispositivos espintrónicos aprovechan el giro de los electrones en lugar de la carga eléctrica para almacenar datos, lo que proporciona una alternativa más eficiente a los chips tradicionales basados en transistores.

Actualmente, el equipo ha estado planeando trabajar con líderes de la industria de semiconductores, incluidos aquellos de Minnesota, para brindar demostraciones a gran escala y producir el hardware para avanzar en la funcionalidad de la IA.

Además de Lv, Wang y Karpuzcu, el equipo incluyó a los investigadores del Departamento de Ingeniería Eléctrica e Informática de la Universidad de Minnesota, Robert Bloom y Husrev Cilasun; al distinguido profesor McKnight y presidente de la cátedra Robert y Marjorie Henle, Sachin Sapatnekar; y a los ex investigadores postdoctorales Brandon Zink, Zamshed Chowdhury y Salonik Resch; junto con investigadores de la Universidad de Arizona: Pravin Khanal, Ali Habiboglu y el profesor Weigang Wang.

Más información:

Yang Lv et al, Demostración experimental de la memoria de acceso aleatorio computacional basada en unión de túnel magnético, npj Computación no convencional (2024). Documento de la investigación: 10.1038/s44335-024-00003-3

Citación:Los ingenieros desarrollan un dispositivo basado en una unión de túnel magnético para que la IA sea más eficiente energéticamente (26 de julio de 2024) recuperado el 26 de julio de 2024 de https://techxplore.com/news/2024-07-magnetic-tunnel-junctionbased-device-ai.html

Este documento está sujeto a derechos de autor. Salvo que se haga un uso legítimo con fines de estudio o investigación privados, no se podrá reproducir ninguna parte del mismo sin autorización por escrito. El contenido se ofrece únicamente con fines informativos.

GIPHY App Key not set. Please check settings